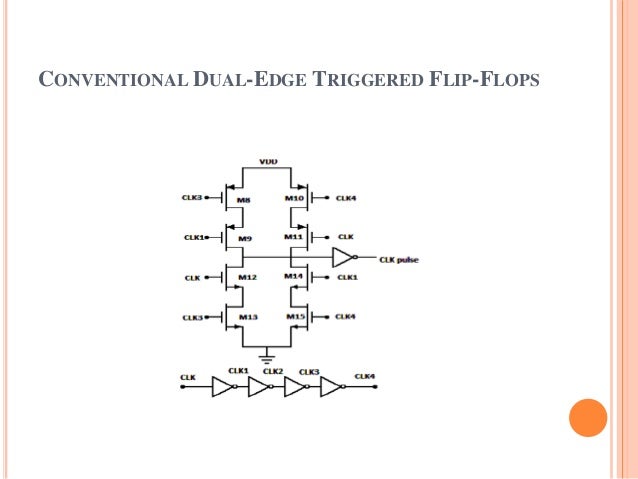

Therefore the proposed DPDET flip-flop is suitable for low supply voltage and high speed CMOS applications. Moreover, the DPDET flip-flop can be used in a 0.9V supply voltage with 224 MHz operating speed. The proposed Double Edge Triggered Flip Flop would be able to respond to both the edges of the clock pulse and would have definite advantages with respect to speed, data transfer rate, reliability and energy dissipation. The power dissipation is reduced about 36 % and 29 % in compared with others for 3.3V and 2.5V supply voltage, respectively. Now, the power consumption of a system becomes a crucial parameter in many applications, hence a Double Edge Triggered Flip Flop is introduced. Double edge-triggered flip-flops (DETFFs) use both edges of the clock to latch data and hence can lead to significant power saving over single edge-triggered flip-flops for a fixed data rate. The operating speed of the DPDET flip-flop is increased about 41 % and 49 % in compared with others for 3.3V and 2.5V supply voltage, respectively.

In implicit-pulse triggered flip-flops (ip-FF), the pulse is generated inside the flip-flop, example, hybrid latch flip-flip (HLFF), semi-dynamic flip-flop (SDFF), and implicit-pulsed data-close-to-output flip-flop (ip-DCO).

#DOUBLE EDGE TRIGGERED FLIP FLOP POWER DISSIPATION GENERATOR#

They are composed of a dual-edge pulse generator and a static flip-flop with equal toggling delays. Here, three new simple architectures are presented for a Dynamic Double Edge Triggered Flip-flop named as Transistor Count Reduction Flip-flop, S-TCRFF (Series Stacking in TCRFF) and FST in TCRFF (Forced Stacking of Transistor in TCRFF). CiteSeerX - Document Details (Isaac Councill, Lee Giles, Pradeep Teregowda): Two Simple structures of low-power Dual-edge triggered Static Pulsed Flip-Flops (DSPFF) are presented in this paper. Because of its single latch structure pulse triggered FF(P -FF) are ore popular tha n conventional type transmission gates. INTRODUCTION In digital circuits FF are the timing elements and they impact largely on circuit speed and power consumption. Based on 0.35um single-poly quad-metal ' CMOS technology, the HSPICE simulation results show that the operating speed of the DPDET flip-flop is 2.7 GHz at a 3.3V supply voltage. Pulse-triggered flip-flops can also be classified into single-edge triggered flip-flops and double-edge triggered flip-flops. Therefore, it is necessary to develop power-efficient circuits. Index terms: - Flip Flop (F F), Low power, Pulse triggered, Edge triggered. The number of transistors is reduced by 40 % to 70 % compared to other double edge triggered flip-flops. The total transistors count is reduced to improve speed and power dissipation in flip-flop. Compared to the previously reported double edge triggered flip-flops, the DPDET flip-flop uses only six transistors with two transistors being clocked, operating correctly under low supply voltage. The DPDET flip-flop uses a split output latch clocked by a short pulse train. In this paper, a low voltage dual-pulse-clock double edge triggered D'flip-flop (DPDET) is proposed.

0 kommentar(er)

0 kommentar(er)